# **Industrial Test of Integrated Circuits**

## Digital Test Training on V93K ATE

### LAB & EXERCISES

### **PART 1:**

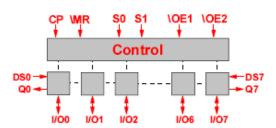

#### **74ACT299 GENERAL DESCRIPTION**

8-bit universal shift/storage register with tristate outputs.

#### **Pin description**

| Pin Names                             | Description                       |

|---------------------------------------|-----------------------------------|

| СР                                    | Clock Pulse Input                 |

| DS <sub>0</sub>                       | Serial Data Input for Right Shift |

| DS <sub>7</sub>                       | Serial Data Input for Left Shift  |

| S <sub>0</sub> , S <sub>1</sub>       | Mode Select Inputs                |

| MR                                    | Asynchronous Master Reset         |

| $\overline{OE}_1$ , $\overline{OE}_2$ | 3-STATE Output Enable Inputs      |

| I/O <sub>0</sub> –I/O <sub>7</sub>    | Parallel Data Inputs or           |

|                                       | 3-STATE Parallel Outputs          |

| Q <sub>0</sub> , Q <sub>7</sub>       | Serial Outputs                    |

#### **Logic diagram**

#### **Truth table**

|    | Inp            | uts            |    | Response                                                                                                                             |

|----|----------------|----------------|----|--------------------------------------------------------------------------------------------------------------------------------------|

| MR | S <sub>1</sub> | S <sub>0</sub> | СР |                                                                                                                                      |

| L  | Х              | Х              | Х  | Asynchronous Reset; Q <sub>0</sub> –Q <sub>7</sub> = LOW                                                                             |

| Н  | Н              | Н              | ~  | Parallel Load; $I/O_n \rightarrow Q_n$                                                                                               |

| Н  | L              | Н              | ~  | Shift Right; $DS_0 \rightarrow Q_0$ , $Q_0 \rightarrow Q_1$ , etc. Shift Left, $DS_7 \rightarrow Q_7$ , $Q_7 \rightarrow Q_6$ , etc. |

| Н  | Н              | L              | ~  | Shift Left, $DS_7 \rightarrow Q_7$ , $Q_7 \rightarrow Q_6$ , etc.                                                                    |

| Н  | L              | L              | Х  | Hold                                                                                                                                 |

- H = HIGH Voltage Level

- L = LOW Voltage Level

- X = Immaterial

- ∠ = LOW-to-HIGH Transition

- Four modes of operation controlled by  $(S_1, S_0)$

- o hold (store)

- o shift left

- o shift right

- o load data

- Asynchronous reset controlled by  $\overline{MR}$  (active on low)

#### **DC Electrical Characteristics (ACT)**

| Symbol           | Parameter                        | $v_{cc}$ | T <sub>A</sub> = | 25°C  | T <sub>A</sub> = -40°C to +85°C | Units | Conditions                               |  |

|------------------|----------------------------------|----------|------------------|-------|---------------------------------|-------|------------------------------------------|--|

| Symbol           | Parameter                        | (V)      | Тур              | Gu    | aranteed Limits                 | Units | Conditions                               |  |

| V <sub>IH</sub>  | Minimum HIGH Level               | 4.5      | 1.5              | 2.0   | 2.0                             | V     | $V_{OUT} = 0.1V$                         |  |

|                  | Input Voltage                    | 5.5      | 1.5              | 2.0   | 2.0                             | l v   | or V <sub>CC</sub> – 0.1V                |  |

| V <sub>IL</sub>  | Maximum LOW Level                | 3.0      | 1.5              | 0.8   | 0.8                             | V     | $V_{OUT} = 0.1V$                         |  |

|                  | Input Voltage                    | 4.5      | 1.5              | 0.8   | 0.8                             | l v   | or V <sub>CC</sub> – 0.1V                |  |

| V <sub>OH</sub>  | Minimum HIGH Level               | 4.5      | 4.49             | 4.4   | 4.4                             | V     | I 50 A                                   |  |

|                  |                                  | 5.5      | 5.49             | 5.4   | 5.4                             | V     | $I_{OUT} = -50 \mu\text{A}$              |  |

|                  |                                  |          |                  |       |                                 |       | $V_{IN} = V_{IL}$ or $V_{IH}$            |  |

|                  |                                  | 4.5      | 0.0001           | 3.86  | 3.76                            | V     | I <sub>OH</sub> = -24 mA                 |  |

|                  |                                  | 5.5      |                  | 4.86  | 4.76                            |       | I <sub>OH</sub> = -24 mA (Note 5)        |  |

| V <sub>OL</sub>  | Maximum LOW Level                | 4.5      | 0.001            | 0.1   | 0.1                             | V     | I 50 A                                   |  |

|                  | Output Voltage                   | 5.5      | 0.001            | 0.1   | 0.1                             | l v   | I <sub>OUT</sub> = 50 μA                 |  |

|                  |                                  |          |                  |       |                                 |       | $V_{IN} = V_{IL}$ or $V_{IH}$            |  |

|                  |                                  | 4.5      |                  | 0.36  | 0.44                            | V     | I <sub>OL</sub> = 24 mA                  |  |

|                  |                                  | 5.5      |                  | 0.36  | 0.44                            |       | I <sub>OL</sub> = 24 mA (Note 5)         |  |

| I <sub>IN</sub>  | Maximum Input Leakage Current    | 5.5      |                  | ± 0.1 | ± 1.0                           | μΑ    | $V_I = V_{CC}$ , GND                     |  |

| I <sub>CCT</sub> | Maximum I <sub>CC</sub> /Input   | 5.5      | 0.6              |       | 1.5                             | mA    | $V_{I} = V_{CC} - 2.1V$                  |  |

| l <sub>OLD</sub> | Minimum Dynamic                  | 5.5      |                  |       | 75                              | mA    | V <sub>OLD</sub> = 1.65V Max             |  |

| I <sub>OHD</sub> | Output Current (Note 6)          | 5.5      |                  |       | <b>-75</b>                      | mA    | V <sub>OHD</sub> = 3.85V Min             |  |

| Icc              | Maximum Quiescent Supply Current | 5.5      |                  | 4.0   | 40.0                            | μΑ    | V <sub>IN</sub> = V <sub>CC</sub> or GND |  |

| l <sub>OZT</sub> | Maximum I/O                      |          |                  |       |                                 |       | $V_{I}$ (OE) = $V_{IL}$ , $V_{IH}$       |  |

|                  | Leakage Current                  | 5.5      |                  | ±0.3  | ±3.0                            | μΑ    | $V_I = V_{CC}$ , GND                     |  |

|                  |                                  |          |                  |       |                                 |       | $V_O = V_{CC}$ , GND                     |  |

Note 5: All outputs loaded; thresholds on input associated with output under test.

Note 6: Maximum test duration 2.0 ms, one output loaded at a time.

#### **Recommended Operating Conditions**

Supply Voltage (V<sub>CC</sub>) (Unless Otherwise Specified)

'AC 2.0V to 6.0V 'ACT 4.5V to 5.0V Input Voltage (V<sub>I</sub>) OV to V<sub>CC</sub> Output Voltage (V<sub>O</sub>) OV to VCC

Operating Temperature (T<sub>A</sub>) 74AC/ACT -40°C to +85°C 54AC/ACT -55°C to +125°C

Minimum Input Edge Rate ( $\Delta V/\Delta t$ )

'AC Devices

V<sub>IN</sub> from 30% to 70% of V<sub>CC</sub> V<sub>CC</sub> @ 3.3V, 4.5V, 5.5V 125 mV/ns

Minimum Input Edge Rate ( $\Delta V/\Delta t$ )

'ACT Devices

V<sub>IN</sub> from 0.8V to 2.0V

VCC @ 4.5V, 5.5V 125 mV/ns

#### AC Operating Requirements & Electrical Characteristics (ACT)

|                |                                                                     | V <sub>cc</sub> | $T_A = -$ | +25°C | T <sub>A</sub> = -40°C to +85°C |       |

|----------------|---------------------------------------------------------------------|-----------------|-----------|-------|---------------------------------|-------|

| Symbol         | Parameter                                                           | (V)             | $C_L = 3$ | 50 pF | C <sub>L</sub> = 50 pF          | Units |

|                |                                                                     | (Note 10)       | Тур       | Guar  | anteed Minimum                  |       |

| te             | Setup Time, HIGH or LOW<br>S <sub>0</sub> or S <sub>1</sub> to CP   | 5.0             | 2.0       | 5.0   | 5.5                             | ns    |

| <b>t</b> н     | Hold Time, HIGH or LOW<br>S <sub>0</sub> or S <sub>1</sub> to CP    | 5.0             | -2.0      | 1.0   | 1.0                             | ns    |

| t <sub>s</sub> | Setup Time, HIGH or LOW<br>I/O <sub>n</sub> to CP                   | 5.0             | 1.5       | 4.0   | 4.5                             | ns    |

| <b>н</b>       | Hold Time, HIGH or LOW<br>I/O <sub>n</sub> to CP                    | 5.0             | -1.0      | 1.0   | 1.0                             | ns    |

| s              | Setup Time, HIGH or LOW<br>DS <sub>0</sub> or DS <sub>7</sub> to CP | 5.0             | 1.5       | 4.5   | 5.0                             | ns    |

| н              | Hold Time, HIGH or LOW<br>DS <sub>0</sub> or DS <sub>7</sub> to CP  | 5.0             | -1.0      | 1.0   | 1.0                             | ns    |

| w              | CP Pulse Width<br>HIGH or LOW                                       | 5.0             | 2.0       | 4.0   | 4.5                             | ns    |

| w              | MR Pulse Width, LOW                                                 | 5.0             | 2.0       | 3.5   | 3.5                             | ns    |

| REC            | Recovery Time, MR to CP                                             | 5.0             | 0         | 1.5   | 1.5                             | ns    |

|                  |                                                                                | Vcc      |     | T <sub>A</sub> = +25°C |      | T <sub>A</sub> = -40° |       |       |

|------------------|--------------------------------------------------------------------------------|----------|-----|------------------------|------|-----------------------|-------|-------|

| Symbol           | Parameter                                                                      | (V)      |     | $C_L = 50 \text{ pF}$  |      | C <sub>L</sub> =      | 50 pF | Units |

|                  |                                                                                | (Note 9) | Min | Тур                    | Max  | Min                   | Max   |       |

| f <sub>MAX</sub> | Maximum Input Frequency                                                        | 5.0      | 120 | 170                    |      | 110                   |       | MHz   |

| t <sub>PLH</sub> | Propagation Delay CP to Q <sub>0</sub> or Q <sub>7</sub> (Shift Left or Right) | 5.0      | 4.0 | 8.5                    | 12.5 | 3.0                   | 14.0  | ns    |

| t <sub>PHL</sub> | Propagation Delay CP to Q <sub>0</sub> or Q <sub>7</sub> (Shift Left or Right) | 5.0      | 4.0 | 9.0                    | 13.5 | 3.5                   | 15.0  | ns    |

| t <sub>PLH</sub> | Propagation Delay<br>CP to I/O <sub>n</sub>                                    | 5.0      | 4.5 | 8.5                    | 12.5 | 4.5                   | 13.5  | ns    |

| t <sub>PHL</sub> | Propagation Delay<br>CP to I/O <sub>n</sub>                                    | 5.0      | 5.0 | 9.5                    | 15.0 | 4.5                   | 16.5  | ns    |

| t <sub>PHL</sub> | Propagation Delay MR to Q <sub>0</sub> or Q <sub>7</sub>                       | 5.0      | 4.0 | 14.0                   | 15.0 | 4.0                   | 18.0  | ns    |

| t <sub>PHL</sub> | Propagation Delay MR to I/On                                                   | 5.0      | 4.0 | 13.0                   | 14.5 | 3.5                   | 17.5  | ns    |

| t <sub>PZH</sub> | Output Enable Time OE to I/On                                                  | 5.0      | 2.5 | 8.0                    | 12.0 | 1.5                   | 13.0  | ns    |

| t <sub>PZL</sub> | Output Enable Time  OE to I/O <sub>n</sub>                                     | 5.0      | 2.0 | 8.0                    | 12.0 | 1.5                   | 13.5  | ns    |

| t <sub>PHZ</sub> | Output Disable Time  OE to I/On                                                | 5.0      | 2.0 | 8.5                    | 12.5 | 2.0                   | 13.5  | ns    |

| PLZ              | Output Disable Time OE to I/On                                                 | 5.0      | 2.5 | 8.0                    | 11.5 | 2.0                   | 12.5  | ns    |

#### 1. Exercise: 74ACT299 – Test patterns for functional test

Referring to the truth table, fill missing instructions in the right column and complete the test vector columns for each pin when necessary (remember that no empty entries are allowed).

| М | СР | S0 | S1  | DS | DS | 10  | 10 | 10 | 10 | 10 | 10 | 10 | 10 | Q | Q | INSTRUCTIONS     |

|---|----|----|-----|----|----|-----|----|----|----|----|----|----|----|---|---|------------------|

| R | •  | •  | 0.1 | 0  | 7  | 0   | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 0 | 7 |                  |

|   |    |    |     |    |    |     |    |    | _  |    |    |    |    |   |   |                  |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   |                  |

| 0 | 1  | 0  | 0   | 1  | 1  | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | Х | Х | Reset            |

| 1 | 1  | 0  | 0   | 1  | 1  | L   | L  | L  | L  | L  | L  | L  | L  | L | L | Hold             |

| 1 | 1  | 1  | 1   | 0  | 0  | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Н | L | // Load 10000000 |

| 1 | 1  | 1  | 0   | 0  | 0  | ــا | Н  | L  | L  | L  | L  | L  | L  | L | L |                  |

| 1 | 1  | 1  | 0   | 0  | 0  | L   | L  | Н  | L  | L  | L  | L  | L  | L | L |                  |

| 1 | 1  | 1  | 0   | 0  | 0  | L   | L  | L  | Н  | L  | L  | L  | L  | L | L |                  |

| 1 | 1  | 1  | 0   | 0  | 0  | L   | L  | L  | L  | Н  | L  | L  | L  | L | L |                  |

| 1 | 1  | 1  | 0   | 0  | 0  | L   | L  | L  | L  | L  | Н  | L  | L  | L | L |                  |

| 1 | 1  | 1  | 0   | 0  | 0  | L   | L  | L  | L  | L  | L  | Н  | L  | L | L |                  |

| 1 | 1  | 1  | 0   | 0  | 0  | L   | L  | L  | L  | L  | L  | L  | Н  | L | Н |                  |

| 1 | 1  | 1  | 0   | 0  | 0  | L   | L  | L  | L  | L  | L  | L  | L  | L | L |                  |

| 1 | 1  | 0  | 1   | 0  | 1  | L   | L  | L  | L  | L  | L  | L  | Н  | L | Н | Shift left 1     |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   | Shift left 1     |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   | Shift left 0     |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   | Shift left 0     |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   | Shift left 0     |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   | Shift left 0     |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   | Shift left 0     |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   | Shift left 0     |

| 1 | 1  | 0  | 0   | 0  | 0  | Н   | Н  | L  | L  | L  | L  | L  | L  | Н | L | Hold             |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   | // Load 10101010 |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   | Hold             |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   | Shift right 0    |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   | Hold             |

|   |    |    |     |    |    |     |    |    |    |    |    |    |    |   |   | Reset            |

| 1 | 1  | 1  | 1   | 0  | 0  | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | Н | Н | // Load 11111111 |

| 1 | 1  | 0  | 0   | 0  | 0  | Н   | Н  | Н  | Н  | Н  | Н  | Н  | Н  | Н | Н |                  |

| 1 | 1  | 1  | 1   | 0  | 0  | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | L | L |                  |

| 1 | 1  | 0  | 0   | 0  | 0  | L   | L  | L  | L  | L  | L  | L  | L  | L | L |                  |

Now you have to write a test pattern which first makes device initialization and verifies the correct initialization, then makes a parallel load all IOs at "1", and finally verifies the shift left function with the serial input DS7 set at "0" until a "L" state can be read out on the serial output Q0.

| М | СР | S0 | S1 | DS | DS | 10 | 10 | 10 | 10 | 10 | 10 | 10 | 10 | Q0 | Q7 | INSTRUCTIONS |

|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------------|

| R |    |    |    | 0  | 7  | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  |    |    |              |

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |              |

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |              |

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |              |

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |              |

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |              |

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |              |

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |              |

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |              |

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |              |

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |              |

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |              |

#### 2. Exercise: 74ACT299 – Values for parametric tests

Referring to DC electrical characteristics, extract the value guaranteed in the datasheet for the following parameters. The conditions are  $T=25^{\circ}C$  and Vcc=4.5V.

| Datasheet guaranteed value |                           |

|----------------------------|---------------------------|

| Vil =                      |                           |

| Vih =                      |                           |

| Vol =                      | with iol=24mA & Vcc=4.5V  |

| Voh =                      | with ioh=-24mA & Vcc=4.5V |

Referring to AC operating requirements and AC electrical characteristics, extract the value guaranteed in the datasheet for the following parameters when T=25°C and Vcc=5V.

| Datasheet guaranteed value      |

|---------------------------------|

| Setup time I/O vs CP =          |

| Setup time DSO/DS7 vs CP =      |

| Setup time SO/S1 vs CP =        |

| Hold time I/O vs CP =           |

| Hold time DS0/DS7 vs CP =       |

| Hold time SO/S1 vs CP =         |

| Propagation delay I/O vs CP =   |

| Propagation delay Q0/Q7 vs CP = |

#### **FIRST STEPS WITH SMARTEST: PART 1**

#### **Step 1: Launching SmarTest**

1/ Open the VNC icon

Ask the teacher your login and refer to the following table to get your password, the VNC display number and the default machine M to use for offline connection.

| Login<br>trainXv93 | Password<br>#trainXv93# | Y: VNC<br>display<br>number | M: Default machine for offline connection |

|--------------------|-------------------------|-----------------------------|-------------------------------------------|

| train1v93          | #train1v93#             | 71                          | verigyon2016                              |

| train2v93          | #train2v93#             | 72                          | verigyon2016                              |

| train3v93          | #train3v93#             | 73                          | verigyoff2017                             |

| train4v93          | #train4v93#             | 74                          | verigyoff2017                             |

| train5v93          | #train5v93#             | 75                          | verigyoff2017                             |

| train6v93          | #train6v93#             | 76                          | verigyoff2017                             |

| train7v93          | #train7v93#             | 77                          | verigyoff2017                             |

| train8v93          | #train8v93#             | 78                          | verigyoff2017                             |

2/ Use this information to fill the VNC Connect window: M.cnfm.fr:Y with M = verigyon2016 OR verigyoff2017

Once the connection established, according to the machine you connected, you should get one of the 2 following windows.

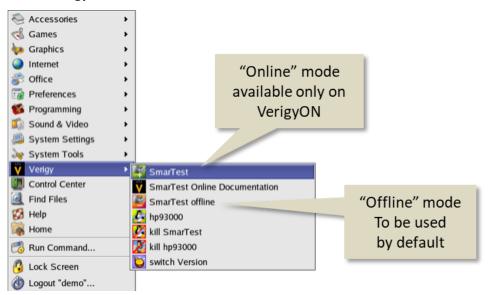

3/ From the start menu « > » (also called RedHat menu), the shortcuts to launch SmarTest® are located in the menu "Verigy" or "Advantest".

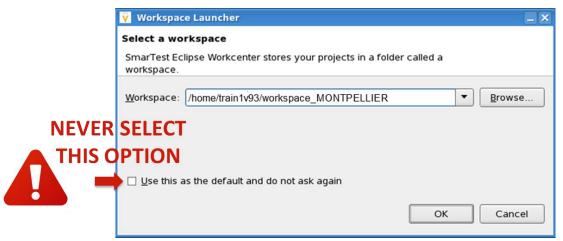

When starting **SmarTest®**, you will have displayed a window called Workspace Launcher window. Select Ok if you have the following path: /home/trainXv93/workspace\_MONTPELLIER; otherwise "Browse" through the directories to access it.

Never save your test program under this path. This is not the expected test program directory. It will induce errors.

When launching **SmarTest**®, 3 windows appear on the screen:

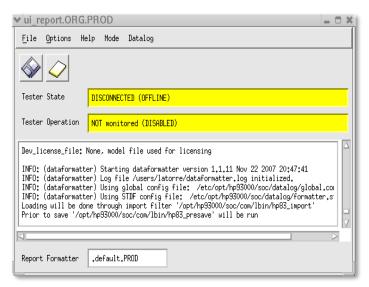

« Operation Control » window allows controlling tasks execution on tester

Used to format datalog stream results.

« ui\_report » window allows following the communication between the tester and SmarTest®.

It is very important to regularly look at this window to verify if any error or warning messages appear.

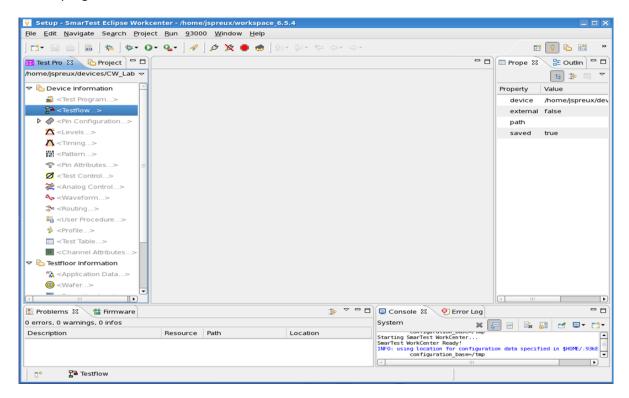

« SmarTest Eclipse Workcenter » window where the users will find all tools to develop a test program.

#### **Step 2: Creating SmarTest Device directory**

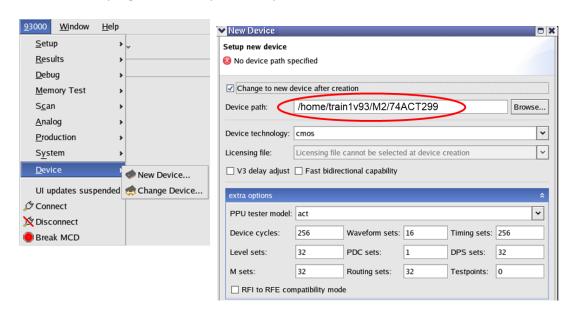

From the tool bar of the "Smartest Eclipse Workcenter" window, select **93000/Device/New Device**; from the opened window, browse the path **/home/trainXv93/M2/** and enter the name **74ACT299** to create the new test program directory (refer to picture below).

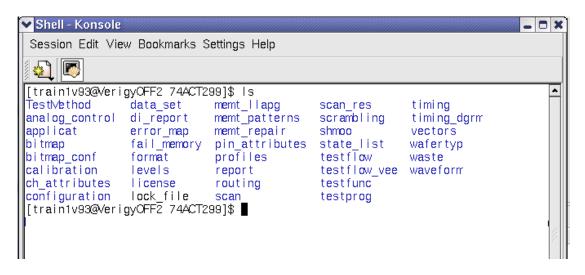

Return to the RedHad menu and open a "Terminal" window from "System Tools".

Type the following command to access to your device directory:

- > cd /home/trainXv93/M2/74ACT299

- > Is (to see all the sub-directories automatically created)

#### Reminder: Procedure to exit SmarTest and VNC

- Exiting SmarTest: click "File > Exit"

- Exiting **VNC**: click on the **cross ☑ (DO NOT LOGOUT!)**

#### FIRST STEPS WITH SMARTEST: PART 2

Now, you are going to setup the basic elements: PINS, LEVELS, TIMING, PATTERN.

#### Step 1: PINS

Depending on the progress of the course, the pin configuration will be either created by the trainees or given by the trainer.

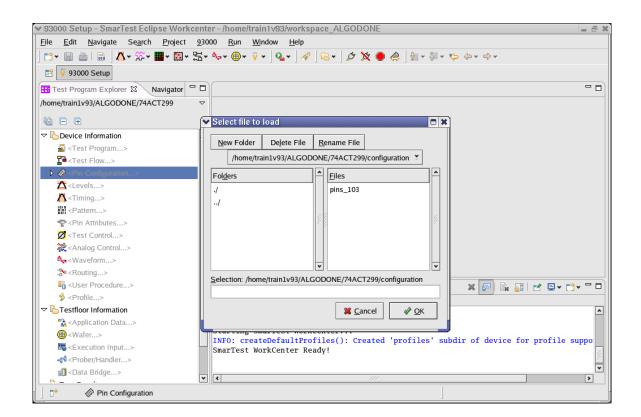

To copy an existing pin configuration file:

- OPEN a terminal window.

- Type the following command:

- > cp /home/trainer/74ACT299/INIT\_FILES/pins\_103 /home/trainXv93/M2/74ACT299/configuration/.

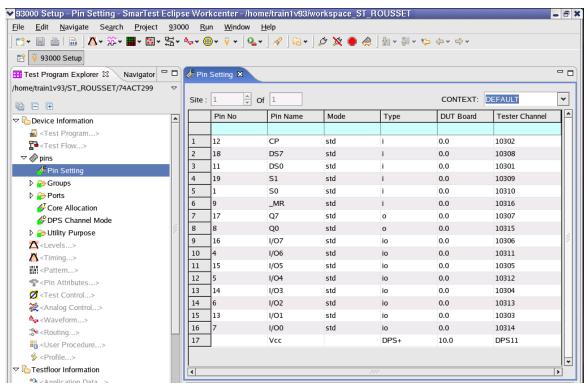

- From the **Test Program Explorer** window on **SmarTest**, select the "**Pin Configuration**" grey item (grey means not loaded). From the right click menu, load this "Pin Configuration" file.

Have a look at the pins and pin groups setup:

#### Step 2: LEVELS

Repeat the operation for the levels:

- Copy an existing levels file to your device level directory with the command:

- > cp /home/trainer/74ACT299/INIT\_FILES/levels\_74ACT299 /home/trainXv93/M2/74ACT299/levels/.

- Return to the Test Program Explorer and load the levels:

- 1. From the Test Program Explorer, select "levels" item

- 2. From the right click menu, select "Load"

- 3. From the "Select File to Load" window, select "levels\_74ACT299"

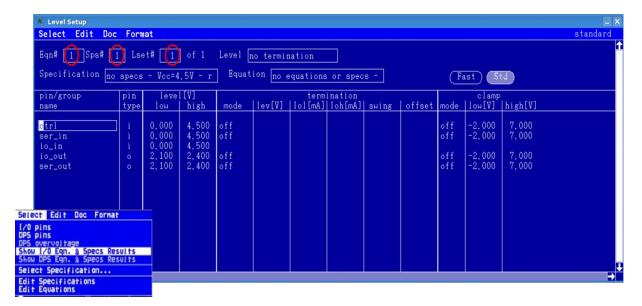

- Open the Level Setup window from the level item in the Test Program Explorer (« open » from the right-click menu or double-click). Displayed values are defaults values.

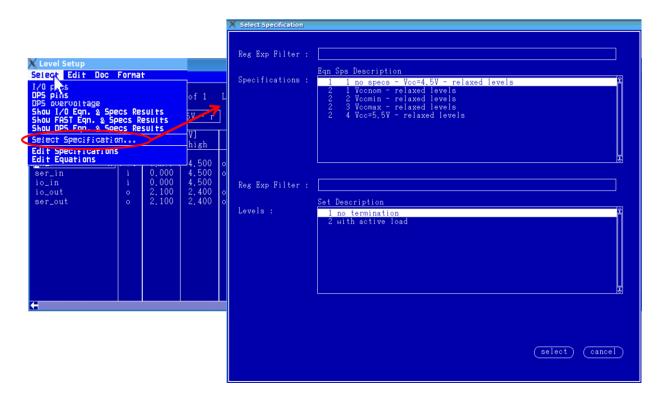

From the menu "Select" of the Level Setup window, choose "Show I/O Eqn & Specs Results" to display the levels that will be applied to the device as specified by Eqn#, Sps# and Lset#.

You can access to the list of existing Eqn#, Sps# and Lset# from the menu "Select->Select Specification..." and choose the one you want to display.

To understand how these values have been programmed:

- Choose "Edit Equations" from the menu "Select" to open the Level Equation Set Editor; look at the defined EQNSETs and LEVELSETs.

```

/var/opt/hp93000/soc/tmp/93k.VsQyEO/edit_lvleqn

□ ×

File Edit Search Preferences Shell Macro Windows

Help

P

K ☐ Rev ☐ RegExp ☐ Case

/var/opt/hp93000/soc/tmp/93k.VsQyEO/edit_lvleqn 1398 bytes

L: --- C: -

71 EQNSET 2 "with specs"

72

73

74 SPECS

75 VCC [V] #supply voltage

76 VIL [V] #low level input voltage

77

78

79

79

70 VOL [V] #low level input voltage

79

70 VOL [V] #low level output voltage

79

70 VOL [V] #low level output voltage

79

80

80

81

81

82 DPSPINS Vcc

83 vout=VCC

84 ilimit=1000

85 t_ms = 4

86 offcurr=act

88 LEVELSET 1 "no termination"

90 PINS ctrl ser_in

91 vil =VIL

92 vih =VIH

93

94 PINS ser_out

95

96 vol= VOL

97 voh = VOH

98

99 PINS io_pins

100

101 vil = VIL

102 vih = VIH

103 vol = VOL

104 voh = VOH

```

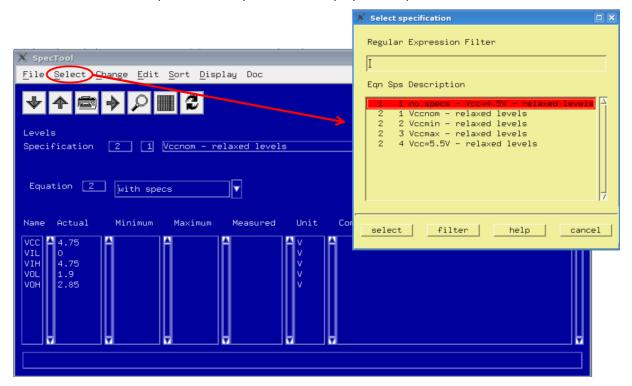

Choose "Edit Specifications" from the menu "Select" to open the Spec Tool; look at the Spec Variables and their values for the different SpecSets.

Use the menu "Select" of the Spec Tool to choose among the list of existing specifications with their description the one you want to display in the Spec Tool.

#### Exercise: 74ACT299 - Basic Elements - Levels

Using the tools/editors available in SmarTest, find the information to fill in the following table.

| Eqn | Spec | Lset | supply    | all_in |        |        |              |        |

|-----|------|------|-----------|--------|--------|--------|--------------|--------|

| #   | #    | #    | DPS value | Drive  | values | Compai | Active Load? |        |

|     |      |      |           | low    | high   | low    | high         |        |

| 1   | 1    | 1    |           |        |        |        |              | Yes/No |

| 1   | 1    | 2    |           |        |        |        |              | Yes/No |

| 2   | 1    | 1    |           |        |        |        |              | Yes/No |

| 2   | 2    | 1    |           |        |        |        |              | Yes/No |

| 2   | 3    | 1    |           |        |        |        |              | Yes/No |

#### Step 3: TIMING

Repeat the operation for the timing:

- Copy an existing timing file to your device level directory with the command:

- > cp /home/trainer/74ACT299/INIT\_FILES/timing\_74ACT299 /home/trainXv93/M2/74ACT299/timing/.

- Return to the Test Program Explorer and load the timing:

- 1. From the Test Program Explorer, select "timing" item

- 2. From the right click menu, select "Load"

- 3. From the "Select File to Load" window, select "timing\_74ACT299"

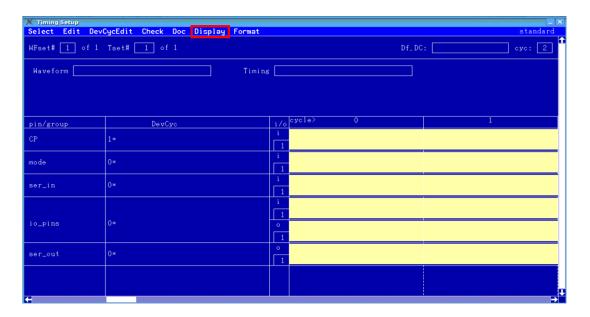

- Open the Timing Setup window from the timing item in the Test Program Explorer ("open" from the right-click menu or double-click).

Select "DISPLAY->DOUBLE" to enlarge the window.

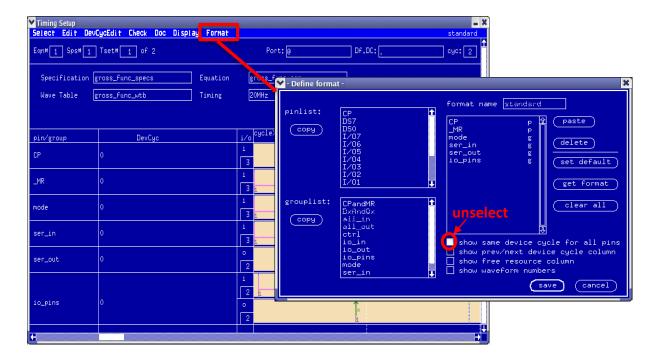

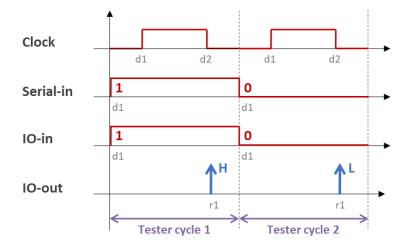

Create an appropriate format to visualize the waveforms for the different types of pin:

- from the menu "Format", choose "new"

- define a format that contains CP, \_MR, mode, ser\_in, ser\_out, io\_pins

- <u>unselect</u> the box "show same device cycle for all pins"

- save your changes

The Timing Setup window now shows one waveform for each pin or pin group defined in the format, as specified by Eqn#, Sps# and Tset#. If it is not the case, choose "Show Eqn & Spec Results" from the menu "Select" and fill the device cycle name you want to display for each pin or pin group in the "DevCyc" column.

To see all the waveforms defined for a given pin or pin group, click on the name of a pin or pin group and choose "One pin" from the menu "Select". It will show you all the defined waveforms for the chosen pin or pin group.

To see again all pins or pin groups, choose again "format pins" from the menu "Select".

To see the values of edge location for a given pin or pin group, click on the name of a pin or pin group and choose "Edge delay" from the menu "Select". It will show you the value of defined edge delays for the chosen pin or pin group.

Note: You can access to the list of existing Eqn#, Sps# and Tset# from the menu "Select->Select Specification..." and choose the one you want to display.

To understand the waveforms displayed in the Timing Setup window:

- look at the waveform table ("edit wave tables" from the menu "Select")

- look at the definition of edges location ("edit equations" from the menu "Select")

- look at the values of the spec variables ("edit specifications" from the menu "Select")

#### Exercise: 74ACT299 - Basic Elements - Timing

Using the tools/editors available in SmarTest, find the information to answer the following questions.

```

Case 1: Eqn# 1, Spec# 1, Tset# 1

Case 2: Eqn# 1, Spec# 1, Tset# 2

Case 3: Eqn# 2, Spec# 1, Tset# 1

Case 4: Eqn# 2, Spec# 2, Tset# 1

Case 5: Eqn# 3, Spec# 1, Tset# 1

```

Which case do not comply with the propagation delay time I/O vs CP given in the datasheet (refer to the value you have extracted from the datasheet, page 6 of this document). Justify your answer.

Which case has the correct waveform format to verify setup or hold times? Justify your answer.

#### **Step 4: PATTERN**

Repeat the operation for the pattern:

- Copy an existing pattern file to your device level directory with the command:

- > cp /home/trainer/74ACT299/INIT\_FILES/pattern\_first\_flow /home/trainXv93/M2/74ACT299/vectors/.

- Return to the Test Program Explorer and load the pattern:

- 4. From the Test Program Explorer, select "pattern" item

- 5. From the right click menu, select "Load"

- 6. From the "Select File to Load" window, select "pattern\_first\_flow"

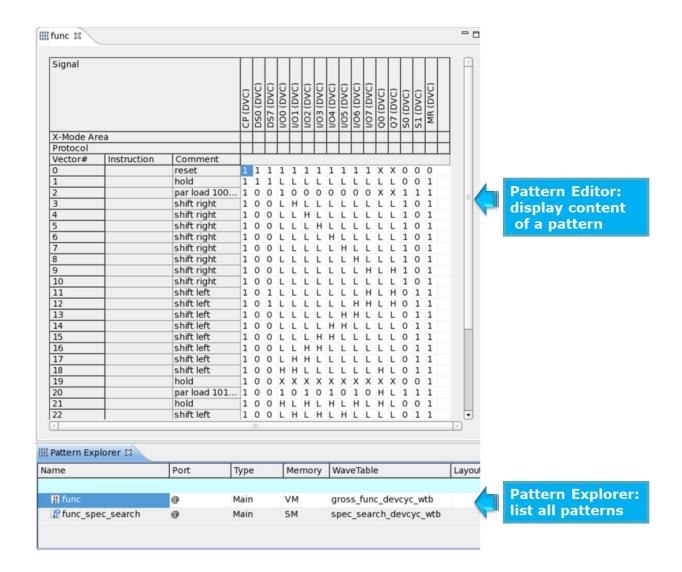

From the Test Program Explorer, double-click on "pattern\_first\_flow" to display the pattern list in **Test Pattern Explorer window**.

For this example, the pattern list only contains 2 patterns.

Double-click on the pattern called "func" and look at the detail of this pattern in the Pattern Editor (you should recognize the pattern from the first exercise).

#### **Reminder: Procedure to exit SmarTest and VNC**

- Exiting SmarTest: click "File > Exit"

- Exiting **VNC**: click on the **cross (DO NOT LOGOUT!)**

#### **QUESTIONS ABOUT FIRST TEST CONCEPTS**

Answer to the following questions relative to the test concepts.

#### Continuity test

What is the purpose of this test?

What is the voltage applied on Vcc and device pins? Why?

The measured voltage on a given pin is 0.004V. What does it mean for this pin?

The measured voltage on a given pin is 2.0V. What does it mean for this pin?

#### **Gross IDD test**

What is the purpose of this test?

What is the voltage applied to Vcc?

What are the voltages applied on inputs for low and high levels?

Referring to DC electrical characteristics, what is the guaranteed limit value for the standby current (at T=25°C)? Indicate whether it is a min or a max value.

| Functional/Structural test                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| What are the voltages applied on inputs for low and high levels in case of a relaxed functional test?                                     |

|                                                                                                                                           |

| What are the comparator threshold voltages typically used for interpretation of low and high levels in case of a relaxed functional test? |

|                                                                                                                                           |

| What are the main differences and similarities between structural and functional test approaches?                                         |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

|                                                                                                                                           |

#### **TEST PROGRAM DEVELOPMENT: FIRST TEST FLOW**

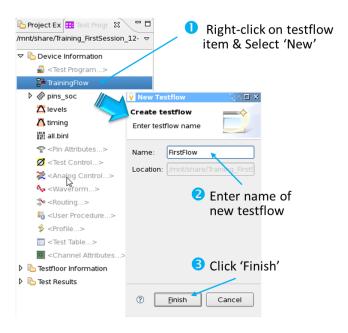

#### Step 5: Create your first test flow

From the **Test Program Explorer** (Setup Perspective), select the "**Testflow"** item. To create a new test flow, perform the following actions:

- From the right click menu, select "New".

- Enter the testflow name "first\_flow" and click "Finish".

From the right click menu on the Testflow item, select "Open with > Flow Sequence Editor".

An empty flow is opened in the flow sequence editor.

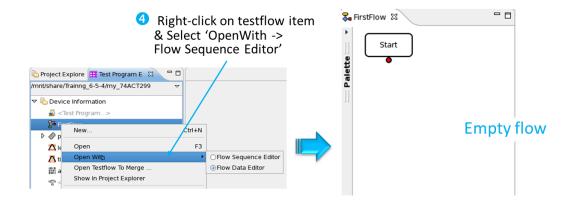

#### Step 6: Setup the context

The next step is to setup the context, i.e. to specify the pins, levels, timing and pattern that will be associated to this test flow. For this, perform the following actions:

- Right-click in an empty zone of the testflow window and select "Open > Setups Page".

- Fill-in your primary files in the corresponding setup entry (pins\_103, levels\_74ACT299, timing\_74ACT299, pattern\_first\_flow).

• Return to Test Program Explorer, select the "**Testflow**" item and select "**Load All Setups**" from the right click menu.

#### **Step 7: Insert Testsuites**

Now you have to insert a test block for each test you want to perform. For this first test flow, you have to implement **4 tests**:

- a continuity test

- a functional test @Vccmin

- a functional test @Vccnom

- a functional test @Vccmax

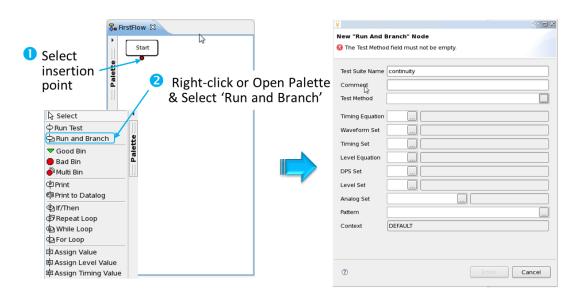

To insert a new Testsuite, perform the following actions:

- Choose the insertion point and select "Insert > run and branch" from the right click menu

- Fill in the required information and click "Finish".

Details on the required information for continuity and functional test blocks are given herafter (choices for timing and pattern information are given but <u>you have to make the appropriate choices regarding level information for each test block</u>).

#### **Continuity test**

TESTSUITE FIELDS VALUE

Testsuite name Continuity

Timing Equation 1

Timing Spec Set 1

Timing Set 1

Level Equation

Level Spec

Level Set

Choose the appropriate Level Spec

Choose the appropriate Level Spec

Choose the appropriate Level Set

Pattern "func"

In the "Test Method" line:

select "dc\_tml>DcTest>Continuity" and click OK.

#### **Functional test**

TESTSUITE FIELDS VALUE

Testsuite name Functional\_Vccmin/nom/max

Timing Equation 1

Timing Spec Set 1

Timing Set 1

Level Equation

Level Spec

Choose the appropriate Level Spec

Level Set

Choose the appropriate Level Spec

Choose the appropriate Level Set

Pattern "func"

#### In the "Test Method" line:

select "ac\_tml > AcTest > FunctionalTest" and click OK.

#### Exercise: 74ACT299 - First Test Flow - Level choices

| Test Block        | Level Equation # | Level Spec # | Level Set # |

|-------------------|------------------|--------------|-------------|

| Continuity        |                  |              |             |

| Functional@Vccmin |                  |              |             |

| Functional@Vccnom |                  |              |             |

| Functional@Vccmax |                  |              |             |

#### **Step 8: Insert Bins**

You have now to insert a bad bin in the failing branch of each test block and a good bin at the end of the test flow according to the information given in the following table.

| BIN TYPE | INSERTION<br>POINT                                  | SOFT<br>BIN<br># | SOFT BIN<br>NAME            | HARD<br>BIN# | HARD BIN NAME |

|----------|-----------------------------------------------------|------------------|-----------------------------|--------------|---------------|

| BAD      | CONTINUITY Failing Branch                           | 2                | FAILED<br>CONTINUITY        | 2            | CONTINUITY    |

| BAD      | FUNCTIONAL Vccmin<br>Failing Branch                 | 3                | FAILED<br>FUNCTIONAL Vccmin | 3            | FUNCTIONAL    |

| BAD      | FUNCTIONAL Vccnom<br>Failing Branch                 | 4                | FAILED<br>FUNCTIONAL Vccnom | 3            | FUNCTIONAL    |

| BAD      | FUNCTIONAL Vccmax<br>Failing Branch                 | 5                | FAILED<br>FUNCTIONAL Vccmax | 3            | FUNCTIONAL    |

| GOOD     | FUNCTIONAL Vccmax Passing Branch (end of test flow) | 1                | PASS                        | 1            | PASS          |

To insert a new Bin, perform the following actions:

- Choose the insertion point and select "Insert > Good/Bad Bin" from the right click menu.

- Fill in the required information and click "Finish".

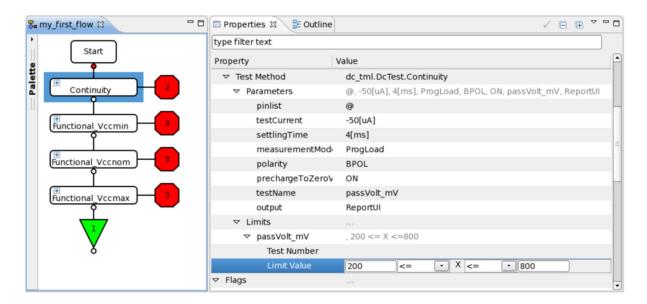

#### **Step 9: Define parameters and limits**

You have to setup the test conditions and limits of your **continuity test block** according to the following information.

| Field            | Value            | Comment       |

|------------------|------------------|---------------|

| pin list         | @                | all pins      |

| test current     | <b>–</b> 50      | uA            |

| pass volt min    | 200              | mV            |

| pass volt max    | 800              | mV            |

| settling time    | 4                | ms            |

| measurement mode | PPMUpar/ProgLoad | (your choice) |

| polarity         | SPOL/BPOL        | (your choice) |

| output           | ReportUI         |               |

Practically to setup the test conditions and limits of a Testsuite, perform the following actions:

- Double-click on the Testsuite in the Test Flow Editor; the Properties View opens.

- In the Properties widow, unfold "Test Methods" (see figure herafter)

- Unfold "Parameters" and replace default values by yours.

- o Unfold "Limits" and replace default values by yours.

Caution: Do not write the units when entering values.

Functional test block takes no test conditions and no test limits (except the pinlist), so you don't have to change the default values.

#### **Step 10: Flag setting and test execution (offline)**

The final step before test execution is to set flags for each Testsuite to specify which results will be displayed in the UI-Report window.

For this, go to the **Properties** view of each Testsuite, unfold "**Flags**" and activate the following options:

- Output on pass

- Output on fail

- Pass value

- Fail value

- Per pin on pass

- Per pin on fail

The tests are now ready to be executed. You have 2 options from the Testflow editor:

- 1. Select a Testsuite and choose **"Run Selected"** from the right click menu. Only this test block is executed.

- 2. Click on any zone of the test flow and choose "Run Testflow" from the right click menu. The complete test flow is executed.

Try both these options and look at the UI-Report window to make sure you have no syntax error and to visualize the displayed results. (Clear the Report window before each execution).

<u>Note</u>: In the offline mode, the Continuity test fails because the simulator returns 0 value for the measured pin voltage. To execute the complete test flow despite this fail, activate the Flag "**Set Pass**" of the continuity test in the **Properties** window. You should obtain a Pass when running the complete test flow.

Your first test flow is now complete and ready to be verified online. For this, quit the simulator mode and connect online to the tester.

Do not forget to disable the Flag "Set Pass" of the continuity test before going to the online mode.

#### Reminder: Procedure to exit SmarTest and VNC

- Exiting SmarTest: click "File > Exit"

- Exiting **VNC**: click on the **cross ☒ (DO NOT LOGOUT!)**

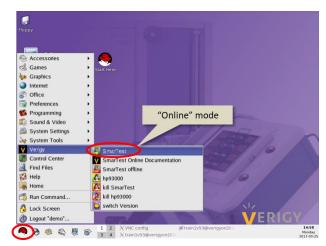

#### Step 11: Online test execution

Connect to the online machine **verigyon2016** using VNC. Keep the same login and password (cf. page 7 to remember your password and VNC display number).

Once the VNC window is opened (purple background), start the online license from the RedHad menu : "Verigy >SmarTest"

In the Test Program Explorer window, check that the test program path is yours (/home/trainXv93/M2/74ACT299). Otherwise, click "93000 > Device > Change Device" and select the path relative to your test program.

From the Test Program Explorer, load your test flow (first\_flow) and all the primary files (pins\_103, levels\_74ACT299, timing\_74ACT299, pattern\_first\_flow).

Open your test flow in the Flow Sequence Editor and perform the following experiments:

- 1. Execute the complete test flow and verify you obtain a PASS.

- 2. Execute only the continuity test and look at the results in the UI-Report window. Do you understand them?

- 3. Return to the **Properties** window of the continuity test and change the "**Polarity**" in the "**Parameters**" section. Execute the test and look at the results in the UI-Report window. Do you understand them?

- 4. Return to the **Properties** window of the continuity test and change the "**MeasurementMode**" in the "**Parameters**" section. Execute the test and look at the results in the UI-Report window. Do you understand them?

- 5. Execute only a functional test and look at the results in the UI-Report window. Do you understand them?

#### **IMPLEMENTATION OF PARAMETRIC TESTS on 74ACT299**

In this lab, you will run a more thorough test flow that includes not only continuity and functional tests but also some DC and AC parametric tests. The structure of the test flow will be provided.

The objective of the exercise is to define the test conditions and limits of the parametric tests according to the device datasheet and to evaluate the actual circuit performances.

Note: to know which test conditions and/or test limits you have to change in each test block, return to page 6 of this document and consult the values you have extracted from the data sheet

#### Step 1: Copy an existing test flow and its associated primary files (offline)

- Open a terminal window from the RedHat menu « ».

- Copy the test flow file called "full\_flow\_2Modify" to your "testflow" directory with the command:

- > cp /home/trainer/74ACT299/INIT\_FILES/full\_flow\_2Modify /home/trainXv93/M2/74ACT299/testflow/.

- Copy the pattern file associated with this test flow to your "vectors" directory with the command:

- > cp /home/trainer/74ACT299/INIT\_FILES/pattern\_full\_flow /home/trainXv93/M2/74ACT299/vectors/.

The levels and timing files used for this full\_flow are the same than for the first\_flow (levels\_74ACT299, timing\_74ACT299).

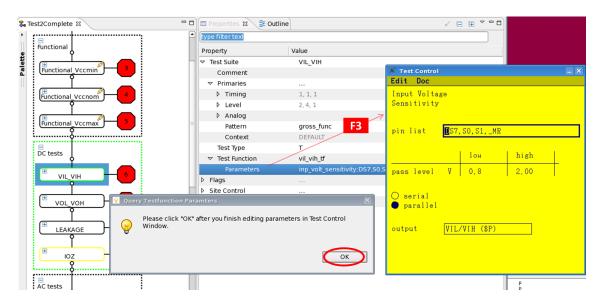

#### Step 2: Modify the existing test flow (offline)

- Load the test flow from the Test Program Explorer and open it in the graphical editor (Flow Sequence Editor).

- Load the primary files associated to this test flow ("Load all setups").

You have now to modify the test flow in order to specify the correct test conditions and limits for the DC and AC tests (Vil/Vih, Vol/Voh, leakage current, setup time, hold time and propagation delay). The modification of the values will be done in the "test control" window (yellow window) for each test block. The procedure is the following:

- Select the first test block you want to modify.

- In the Properties window, select "Test Function > Parameters" and press F3. This will open the "test control" window.

- Change the default values by the values you have extracted from the datasheet. Don't apply any change in the pin list.

- Once the changes are done, close the "test control" window and move to the next test block in the test flow.

You have to modify the following test blocks:

- 1 Vil/Vih test:

only Vil and Vih values matter.

1 Vol/Voh test:

Vol/Voh + Iol/Ioh values have to be considered.

The test control block also asks low/high limits for PMU clamp voltage; enter 0V and 5V respectively.

- 3 setup time tests:

- o DSO/DS7 (ser\_in) versus CP

- o IO[0:7] versus CP

- o SO/S1 (mode) versus CP

- 3 hold time tests:

- o DSO/DS7 (ser\_in) versus CP

- o IO[0:7] versus CP

- o SO/S1 (mode) versus CP

- 2 propagation delay tests:

- o Q0/Q7 (ser\_out) versus CP

- o IO[0:7] versus CP

Once you have modified all the test blocks, save the new test flow under the name "full\_flow" (click right on the test flow item in the Test Program Explorer and select choose "save as").

#### Step 3: Run the test flow (offline)

Run the test flow offline to verify that you don't have any syntax error.

<u>Note</u>: In the offline mode, a Fail might be obtained at any of the parametric tests because the simulator returns dummy values, and the test flow stops at the Fail result. In order to verify the syntax of the entire test flow, you should permit the complete execution of the test flow.

For this, perform the following actions:

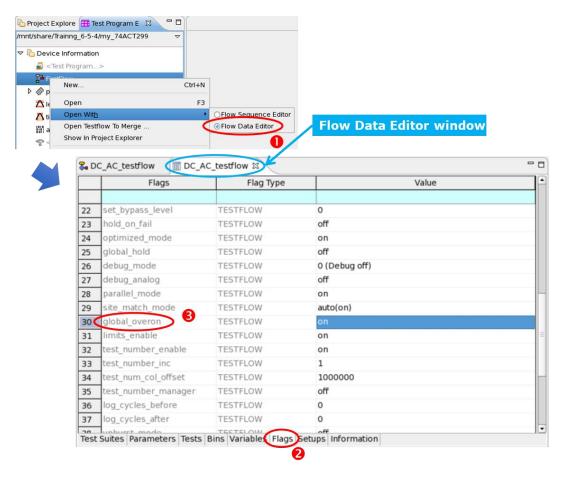

- Open the test flow in the "Flow Data Editor" (click right on the test flow item in the Test Program Explorer and select "Open with > Flow Data Editor").

- Choose the "Flags" tab at the bottom of the window.

- Search the "Global Overon" flag and change its value it to "on". This will enable to continue the execution of the test flow until the final bin, even after reaching a "Bad" bin.

Return to the **Flow Sequence Editor** and run again the entire test flow. All test blocks are now executed, i.e. they all have a Pass or Fail result (as indicated by the green/red color of each test block).

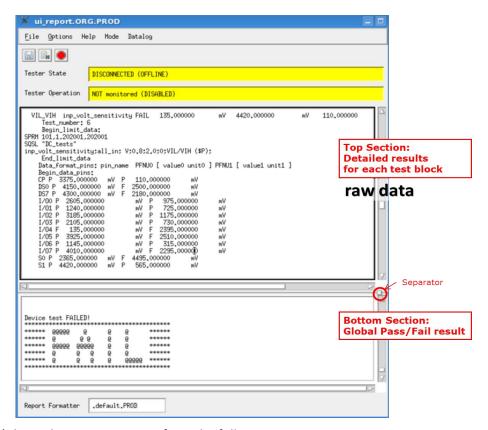

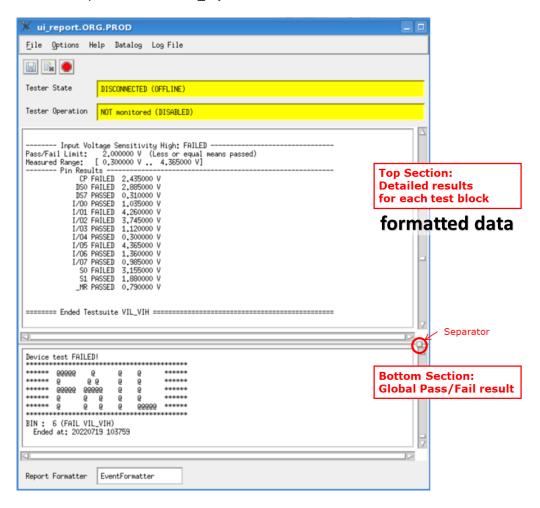

Look at the results in the **UI-report** window. You should have two sections, the bottom section with the global Pass/Fail result and the top section with the detailed results for each test block. Separator between the 2 sections can be moved from the small square on the right side.

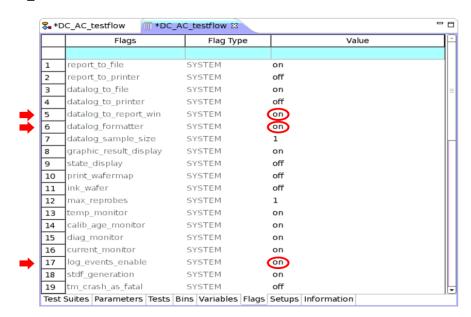

If you don't have the top section, perform the following actions:

- Open the test flow in the "Flow Data Editor" (click right on the test flow item in the Test Program Explorer, select "Open with > Flow Data Editor") and choose the "Flags" tab.

- Make sure that the flags "datalog\_to\_report\_win", and "datalog\_formatter" and "log event enable" are set to "on".

- Make sure that the flags "datalog\_to\_report\_win", and "datalog\_formatter" and "log\_event\_enable" are set to "on".

• Return to the **Flow Sequence Editor** and run again the entire test flow. You should now have the two sections.

<u>Note</u>: The default format used to display the detailed results in the UI-report window is a raw format that does not help to data readability.

To improve data readability, you can specify the use of a formatter with the following actions:

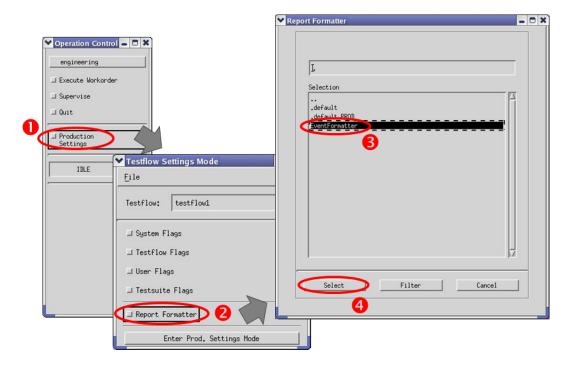

• Go to the "Operation Control" window. Click on "Production Settings", then click on "Report Formatter", choose "EventFormatter" and finish with "Select".

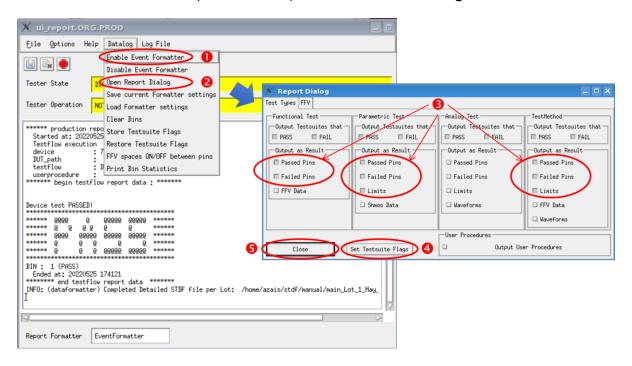

Go to the "UI-report" window. In the "Datalog" menu, choose "Enable Event Formatter". Then choose "Open Report Dialog". For each test type (except the analog one), select "Passed Pins", "Failed Pins" and "Limits" (when available). Click on "Set Testsuite Flags" and finish with "Close".

• Return to the **Flow Sequence Editor** and run again the entire test flow. Look at the detailed results in the top section of the **UI\_report** window. The data are now much easier to read...

Once all these steps are accomplished and everything is ok, your testflow is ready to be executed online. Quit the offline license. Do not forget to disable the Flag "Global Overon" in the Flow Data Editor before going to the online mode.

#### **Step 4: Run the test flow (online)**

- Connect to verigyon2016 and launch the online license.

- Load your test flow, open it in the graphical editor and load the primary files associated to this test flow ("Load all setups").

- Execute the test flow.

- Look at the global Pass/Fail result in the bottom part of the UI-report window. You should obtain a Pass!

- Look at the detailed results in the top part of the **UI-report** window. If data are not correctly formatted, repeat the procedure described in the preceding page to specify the use of a formatter and run again the entire test flow.

- Save the detailed results given in the top section of **UI-report** window in a text file (click in the top section and then click on menu "File > Save") and **quit the online license**.

#### Exercise: 74ACT299 – AC\_DC\_testflow – Test Results

From the analysis of the detailed results saved in the text file, write in the following table the **worst-case values** observed over the tested pins for each measurement. Evaluate the corresponding margin based on the datasheet information.

$$Margin~(\%) = \frac{(Measured~Value~\pm~DS~Limit)}{DS~Limit} * 100$$

| Measurement                        | Worst-case value | Datasheet<br>guaranteed value | Margin (%) |

|------------------------------------|------------------|-------------------------------|------------|

| VIL                                |                  |                               |            |

| VIH                                |                  |                               |            |

| VOL                                |                  |                               |            |

| VOH                                |                  |                               |            |

| Setup time<br>Ser_in to CP         |                  |                               |            |

| Setup time<br>IOx to CP            |                  |                               |            |

| Setup time<br>Mode to CP           |                  |                               |            |

| Hold time<br>Ser_in to CP          |                  |                               |            |

| Hold time<br>IOx to CP             |                  |                               |            |

| Hold time<br>Mode to CP            |                  |                               |            |

| Propagation delay<br>CP to Ser_out |                  |                               |            |

| Propagation delay<br>CP to IOx     |                  |                               |            |

Looking at these results, what can you say about the device?

#### **QUESTIONS ABOUT PARAMETRIC TESTS**

| Answer to the  | following    | questions | relative to  | parametric tests   |

|----------------|--------------|-----------|--------------|--------------------|

| Allowel to the | · IUIIUVVIII | uucsuuns  | I CIALIVE LO | Datailletiit tests |

#### Vil/Vih tests

What is the purpose of Vil/Vih test?

Observe the VIL/VIH measurements displayed in the table below.

| PIN | VIL        | VIH        |

|-----|------------|------------|

| DS7 | 1.500000 V | 1.785000 V |

| S0  | 1.395000 V | 1.825000 V |

| S1  | 1.455000 V | 1.845000 V |

| _MR | 1.435000 V | 1.740000 V |

According to the data sheet values, do you think these tests pass at T°=25C? Justify your answer.

#### Vol/Voh tests

What is the purpose of Vol/Voh test?

Referring to the datasheet, how many Vol/Voh tests should be implemented to exhaustively verify all Vol/Voh specifications? List them.

#### Leakage tests

Explain the condition on Vcc.

How do you manage the Iil/Iih test if you have classic input pins and pull-up ones?

#### Setup and hold time tests

Do you agree with both definitions?

- The setup time is the maximum amount of time the data input must be held steady before the activation of the clock.

- The hold time is the minimum amount of time that the data have to be present before the activation of the clock.

If not, provide the correct definition.

Look at setup time measurements displayed in the table below.

| PIN | SETUP TIME  |

|-----|-------------|

| 100 | 3.493000 ns |

| 101 | 3.431000 ns |

| 102 | 3.294000 ns |

| 103 | 3.210000 ns |

| 104 | 3.227000 ns |

| 105 | 3.232000 ns |

| 106 | 3.192000 ns |

| 107 | 3.393000 ns |

According to the datasheet values, do you think this test passes at T°=25C? Justify your answer.

#### **Propagation delay tests**

What is the purpose of the propagation delay test?

Do the following measurements meet the specifications?

| PIN | Prop delay   |

|-----|--------------|

| Q7  | 9.701000 ns  |

| Q0  | 10.535000 ns |

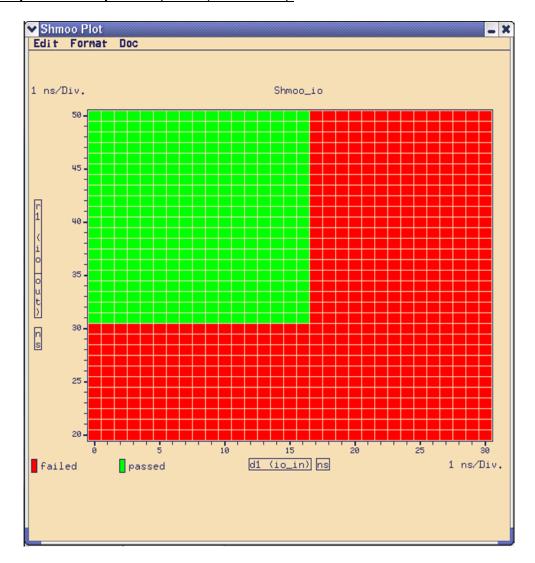

#### **QUESTIONS ABOUT SHMOO PLOT ANALYSIS**

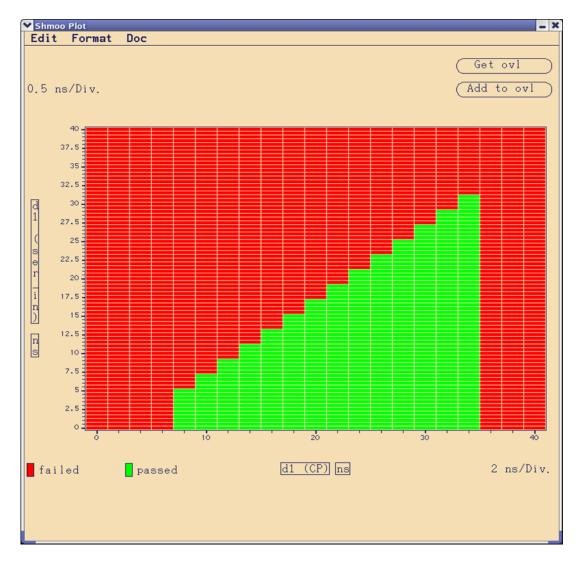

What are the objectives of performing shmoo plots?

You have to analyse the 2 shmoo plots presented hereafter using the following procedure:

- 1. Identify the parameters that are varied on the X and Y axis and their variation range.

- 2. Observe the Pass/Fail frontier and identify the threshold value of both parameters for each P/F area. Does the circuit comply with the datasheet specifications? If possible, evaluate the margin with respect to datasheet specifications.

- 3. Explain what the shmoo plot reveals about the circuit behavior.

#### 1. Analysis of shmoo plot n° 1 (Vcc=5V):

#### 2. Analysis of shmoo plot n° 2 (Vcc=5V, d1-CP=20ns):

## **PART 6:**

#### **TEST FLOW DEBUG**

In this lab, you will use the tools provided in SmarTest (Error Map, Pattern Debugger, Timing Diagram) to debug a test flow in which programming errors have been intentionally introduced.

Depending on the progress of the course, this lab will be done either by the trainees alone, or interactively with the trainer.

#### Step 1: Copy an existing test flow (offline)

- Open a terminal window from the RedHat menu « ».

- Copy the test flow file called "full\_flow\_2Debug" to your testflow directory with the command:

- > cp /home/trainer/74ACT299/INIT\_FILES/full\_flow\_2Debug /home/trainXv93/M2/74ACT299/testflow/.

- Copy the primary files associated with this test flow to the proper directories with the commands:

- > cp /home/trainer/74ACT299/INIT\_FILES/levels\_2Debug /home/trainXv93/M2/74ACT299/levels/.

- > cp /home/trainer/74ACT299/INIT\_FILES/timing\_2Debug /home/trainXv93/M2/74ACT299/timing/.

- > cp /home/trainer/74ACT299/INIT\_FILES/pattern\_2Debug /home/trainXv93/M2/74ACT299/vectors/.

#### Step 2: Run and debug the test flow (online)

- Connect to verigyon2016 and launch the online license.

- Load the test flow, open it in the graphical editor and load the primary files (pins\_103, levels\_2Debug, timing\_2Debug, pattern\_2Debug).

- Run and debug the test flow using any tool available in SmarTest. After your modifications, you should obtain a Pass!

#### Results – Test Flow Debug

Detail your observations and modifications in the following table.

| Failing Testsuite<br>Name | Identified Problem | Correction |

|---------------------------|--------------------|------------|

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

|                           |                    |            |

#### **Exercise: FOCUS ON FAULT DIAGNOSIS**

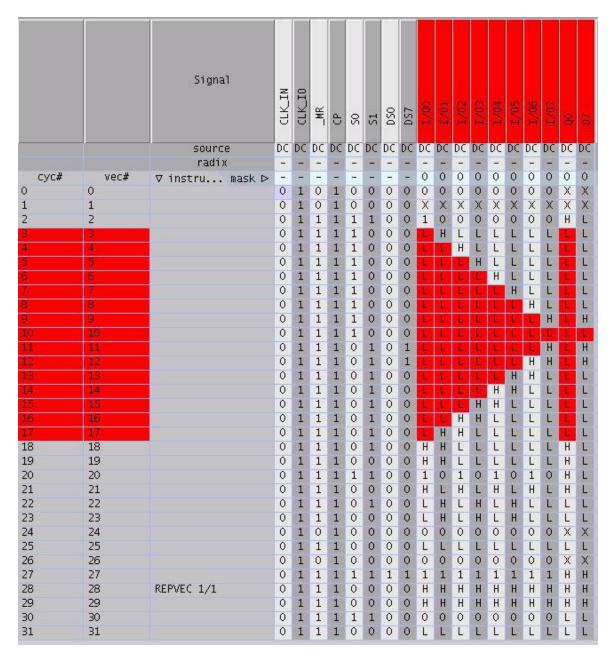

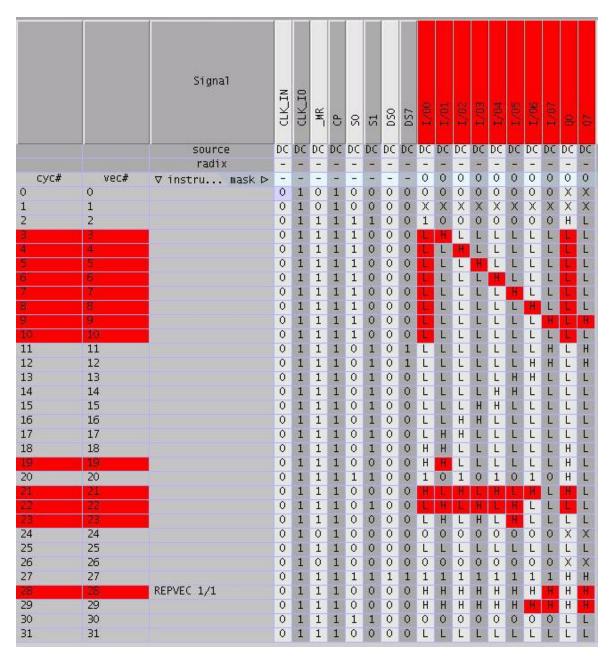

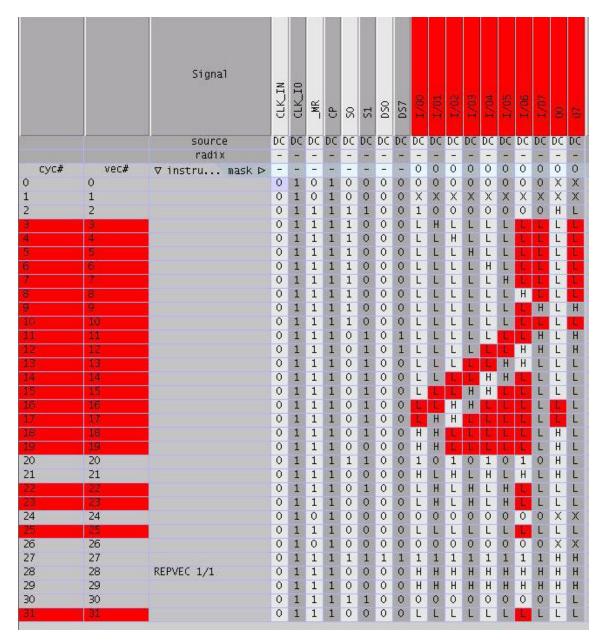

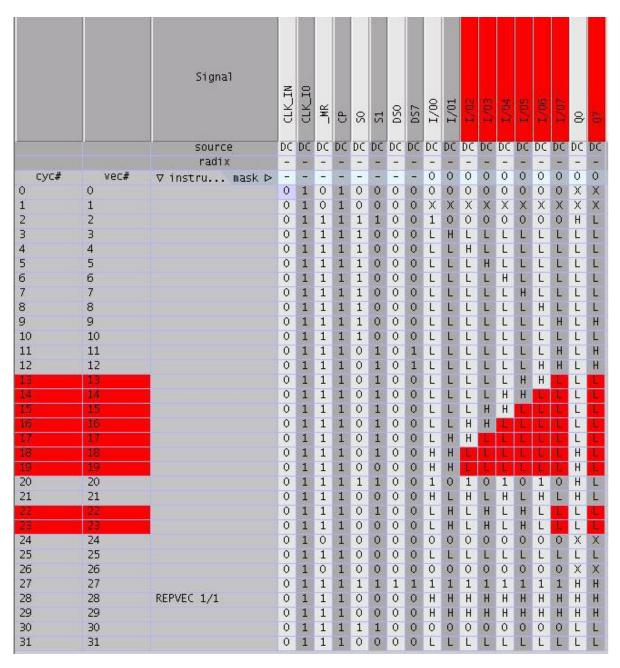

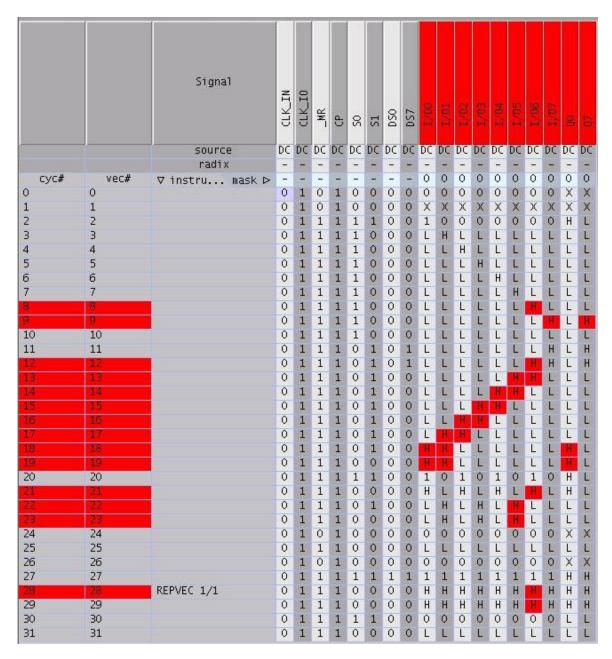

In this section, faults have been inserted in the device using the FPGA board approach. Using the pattern debugger tool of the tester, we have collected the resulting failing cycles and failing pins in the test pattern. Each red box corresponds to a failing cycle + failing output pin. The value in the box corresponds to the expected data on the output pin, not the captured one.

From the given pattern reports and without using any tool, found the type of fault (stuck at 0 or 1) and the faulty pin. Each pattern report corresponds to a single stuck at fault introduced on one of the following pins: IO/1, IO/5, IO/6, DS0, DS7, S0, S1 and CP.

Fill the following table with your results. For each pattern report, detail your analysis (Observation > Hypothesis > Conclusion).

| Pattern Report     | Stuck-at-1 | Stuck-at-0 | Faulty pin |

|--------------------|------------|------------|------------|

| Pattern report n°1 |            |            |            |

| Pattern report n°2 |            |            |            |

| Pattern report n°3 |            |            |            |

| Pattern report n°4 |            |            |            |

| Pattern report n°5 |            |            |            |